kaiyun通过Level和Step两方面剖析现代电子集成技术集成的三个层次。每一个层次的集成,都分为不同的环节。这篇文章,我们从层次-Level和环节-Step两个方面来剖析现代电子集成技术。

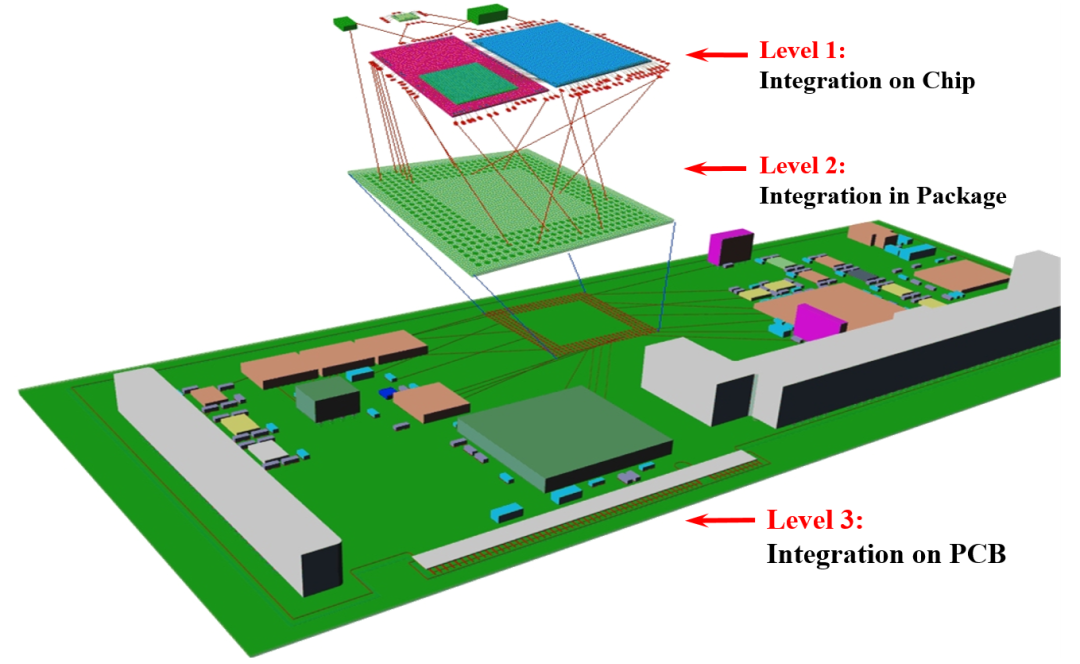

电子系统的集成主要分为三个层次(Level):芯片上的集成,封装内的集成,PCB板级集成,如下图所示:

芯片上集成的基本单元是晶体管Transistor,我们称之为功能细胞 (Function Cell),大量的功能细胞集成在一起形成了芯片。 封装内集成的基本单元是上一步完成的裸芯片或者小芯片Chiplet,我们称之为功能单元 (Function Unit),这些功能单元在封装内集成形成了SiP。 PCB上集成的基本单元是上一步完成的封装或SiP,我们称之为微系统(MicroSystem),这些微系统在PCB上集成为尺度更大的系统。 可以看出,集成的层次是一步步进行的,每一个层次的集成,其功能在上一个层次的基础上不断地完善,尺度在也不断地放大。

到了PCB这一层次,电子系统的功能已经比较完备,尺度也已经放大适合人类操控的地步,加上其他的部件,就构成了人们最常用的系统——常系统 (Common System),例如我们每天接触的手机电脑。

功能细胞的数量也成为系统先进性的重要标志,的细胞数量为40~60万亿,系统如果要想真正成为像人一样智能的系统,其包含的功能细胞或许也要达到相同的量级。

为了集成更多的功能细胞,晶体管只能越做越小。现在的晶体管尺寸可能只有最初晶体管刚发明时尺寸的亿万分之一,而其基本功能却是没有变化的。

芯片上的集成,首先要制造出功能细胞,并将它们集成在一起,这些作为功能细胞的晶体管是怎么制造出来并集成在一起的呢?从极简的视角来说,我们需要了解三类材料和三类工艺。

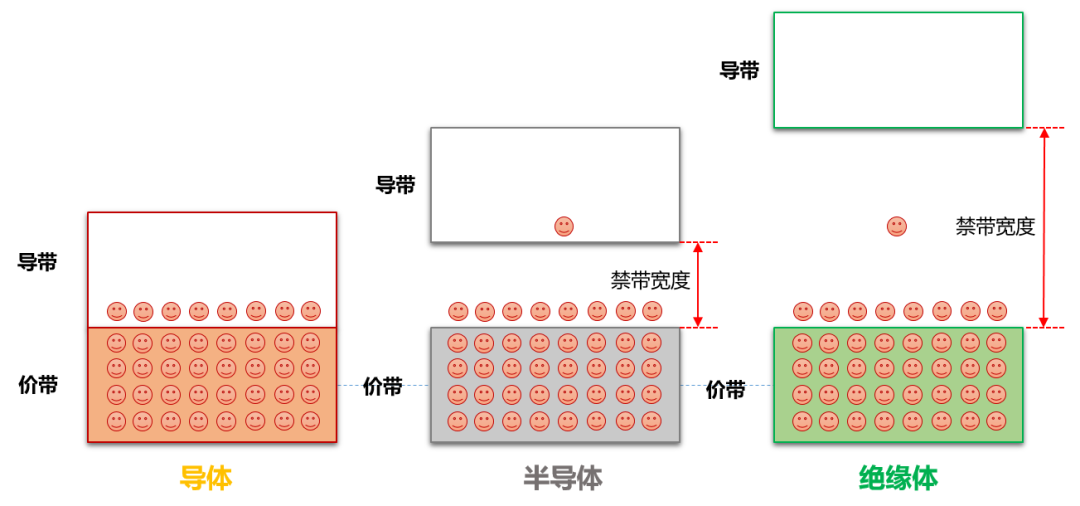

虽然芯片上的材料非常多,现代集成电路中用到的材料几乎要穷尽元素周期表,所有的材料可以分为三大类:导体、半导体、绝缘体。 导体负责传输电子,绝缘体负责隔离电子,其中最重要的自然是半导体,因为它是可变的,它有时候变成导体(导通),允许电子通过,有时候可变成绝缘体(关断),阻隔电子通过。并且,这种变化是可控的,通过设计特别的结构,并施加电流或者电压来控制。 在导体中,导带与价带重叠,其中不存在禁带,电子容易产生移动,在外加电场下形成电流;在半导体中,少部分电子可以跃迁到导带,并在外加电场下形成电流;在绝缘体中,电子无法越过禁带,因而无法形成电流。

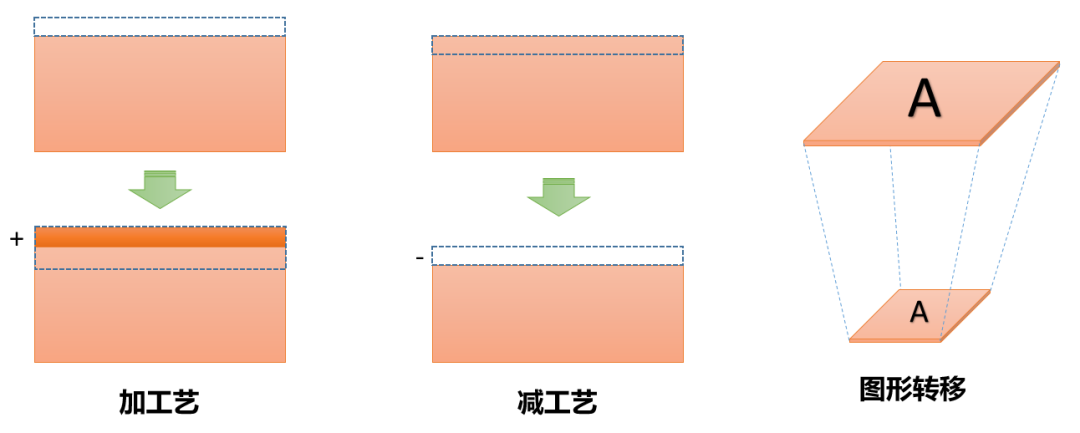

制造芯片的工艺很多,完成一颗芯片制造的工艺流程多达上千种,这些工艺可以分为三大类:加工艺,减工艺,图形转移。

加工艺简单来说就是在基底上增加材料,例如,离子注入,溅射、化学气相沉积CVD,物理气象沉积PVD等都可以归类为加工艺。

图形转移是三类工艺里面最多且最难的,因为每一步的加工艺或者减工艺基本都要以图形转移为依据。图形转移就是将设计的出来的图形,转移的晶圆上,涉及到的是掩膜、光刻、光刻胶。

这些图形多层叠加,将半导体、导体、绝缘体三类材料组合在一起形成特定的立体结构,在晶圆平面创造出功能细胞,实现了相应的功能。

三类材料 + 三类工艺就能造就如此复杂的芯片,也真应了古人讲的“一生二,二生三,三生万物”。

数千道工序之后,芯片上集成的产品是晶圆,晶圆被切割后就形成了芯片Chip或者芯粒Chiplet,为下一个层次的集成做准备。

并非所有的芯片或者芯粒都需要在封装内进行集成,单芯片也可以直接封装并应用在PCB板上。然而,随着摩尔定律日渐失效,封装内的集成越来越受到重视,SiP、先进封装、Chiplet、异构集成、2.5D、3D等概念日益成为业内关注的焦点,封装内的集成终于迎来了春天。

封装内集成不会用到半导体的特性,因此封装内集成所用的材料主要分为两大类:导体和绝缘体,集成的主要目的就是将上一层次(芯片上的集成)所完成的芯片或芯粒在封装内集成并进行电气互联,形成微系统。 最初的封装都是单芯片的,并没有集成的概念,传统的单芯片封装的主要作用有三个:芯片保护、尺度放大kaiyun、电气连接。 以SiP为代表的多芯片封装在传统封装的基础上又增加了3个功能:提升功能密度,缩短互连长度,进行系统重构。 封装内的集成缓解了芯片上集成的压力,从而被看作延缓摩尔定律终结的神兵利器。 封装内的集成由于不需要制造功能细胞(Transistor),而只是将功能单元(chiplet)组装起来,因此其集成的难度被芯片上的集成要低不少。 封装内集成的另一个特点就是灵活度高,可分为2D、2D+、2.5D、3D、4D五种集成的维度。 封装内集成的结果就是形成以SiP、先进封装为代表的功能单元,我们可以称之为微系统。

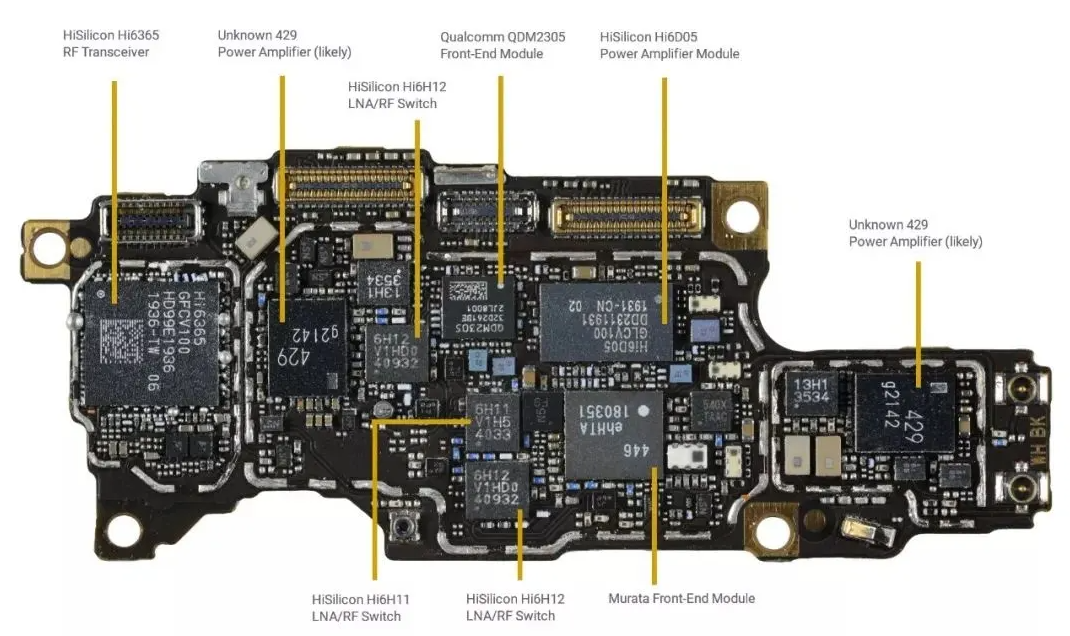

从电子集成的历史来说,PCB上的集成应该是最早出现的,PCB的出现比封装早了11年,比集成电路早了22年。 PCB出现之前,元器件都是用电线直接连接的,除了非常凌乱,集成密度也是难以提升的。 虽然和集成电路以及封装相比,PCB出现的历史最早,但由于受封装尺寸和封装引脚密度的制约,PCB上集成技术的发展相对比较缓慢,从最初的单面板发展到双面板、多层板,组装工艺也由插装式发展为表面贴装SMT,组装密度也越来越高。 今天,PCB上基本都是双面安装元器件,板层也能达到几十层,高密度HDI板、刚柔结合板,微波电路板,埋入式器件板等都在广泛应用。 和封装内的集成一样,PCB上集成也不会用到半导体的特性,因此所用的材料主要分为两大类:导体和绝缘体。集成的主要目的就是将上一层次(封装内的集成)所完成的微系统模块再次集成并进行电气互连,并和其他部件一起,形成常系统,例如我们常用的手机和电脑。

上面我们讲述了电子系统的集成的三个层次:芯片上的集成,封装内的集成,PCB板级集成。每一个层次的集成,都分为不同的环节。

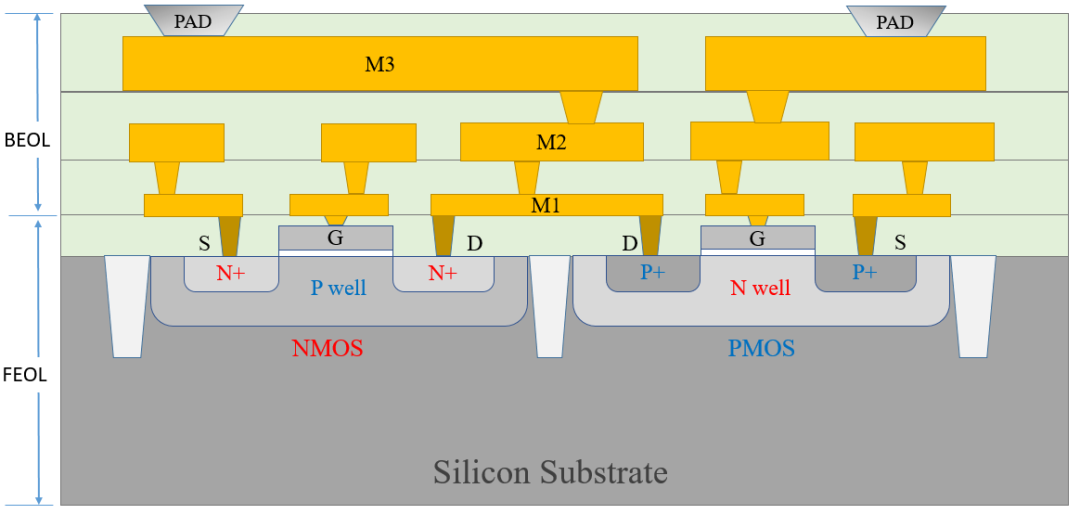

芯片上的集成主要分为两大环节:器件制造和金属互连,也称为前段工艺FEOL和后段工艺BEOL。

器件制造就是在单晶硅片上通过光刻、刻蚀,离子注入,溅射、化学气相沉积,物理气象沉积、化学机械抛光、晶圆整平等工艺步骤,制造出被我们称为功能细胞的晶体管、电阻电容二极管等。现在的5nm工艺可以在1mm²毫米的面积上制造出超过1亿只以上的晶体管。

晶体管的制造过程,主要包括隔离、栅结构、源漏、接触孔等形成工艺,一般称之为前段工艺(FEOL, Front End of Line)。

单晶硅通过离子注入可形成,N、N+、N-,P、P+、P-等多种不同参杂浓度的半导体,多晶硅则作为栅极或者电阻使用。

下图所示为FinFET晶体管在显微镜下的照片,其中较高的白色横梁为栅极G,矮横梁为Fin,其宽度约为栅极宽度的0.67倍,栅极的两侧为源级S和漏极D。

晶体管层制造好后,通过钨等金属制造接触孔contact连接晶体管和首层布线,然后通过多层金属布线和过孔进行电气互连,早先的芯片用铝布线,现在的芯片多用铜布线。 用于连接晶体管等器件的多层金属布线的制造,主要包括互连线间介质沉积,金属线的形成,引出焊盘形成,一般称为后段工艺(BEOL, Back End of Line)。 金属互连中采用的导体有钨、铜、铝等金属,绝缘体则有氧化硅,氮化硅,高介电常数膜,低介电常数膜,聚酰亚胺等。 下图所示为芯片上的金属互连线在显微镜下的照片,可以看出多层布线结构,目前的工艺可以支持超过10层以上的金属布线。 越是先进的集成电路工艺,由于结构尺寸越来越小,各种效应层出不穷,为了解决这些效应,制造出功能正常的晶体管,所用的元素种类越来越多,几乎是一场穷尽元素周期表的运动。 下图给出了前段工艺FEOL和后段工艺BEOL的结构示意图,先在硅基底上制造晶体管,然后通过金属互连将它们连接起来并引出到芯片的PAD。

早先的封装比较简单,主要起着芯片保护、尺度放大、电气互连的作用。其示意图大致如下,通过键合线Bond Wire将芯片的PAD连接到封装基板或者引线框架,然后再连接到外部引脚,通过引脚的排列方式,可分为BGA,CGA,QFP,LCC,SOP,DIP等多种封装形式。

传统的封装由于内部结构比较单一,都是用键合线将芯片引脚连接的引线框架或者基板,而外部引脚排布方式却多样化,因此人们谈论起封装,津津乐道的就是其外部的各种封装形式。因此我们说:传统封装重外不重内。而到了SiP和先进封装时代,这种情况发生了巨大的改变,SiP和先进封装其外部封装形式逐渐统一到引脚排布更多、互连密度更大的BGA,CGA等封装形式,而封装内部由于有了集成的功能,其结构变得越来越复杂,人们对封装的关注逐渐由外部的封装形式转变为内部的封装结构。因此我们说:先进封装重内不重外。 为了提高封装内的功能密度,需要在封装内集成更多的功能单元,传统的键合线连接方式已经无法满足要求,人们发明出多种多样的先进封装技术,下面我们就看看其中最为典型的技术。

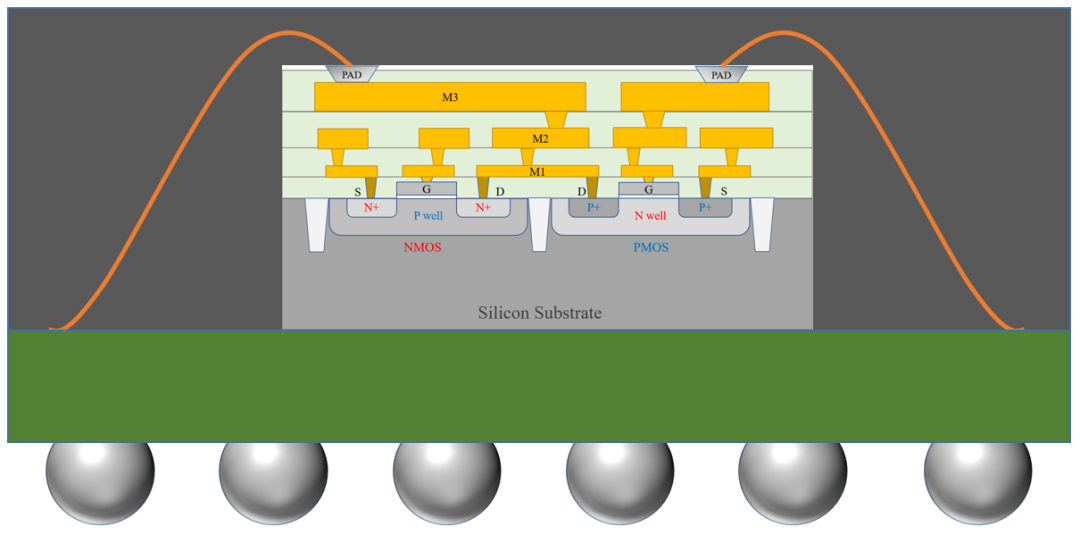

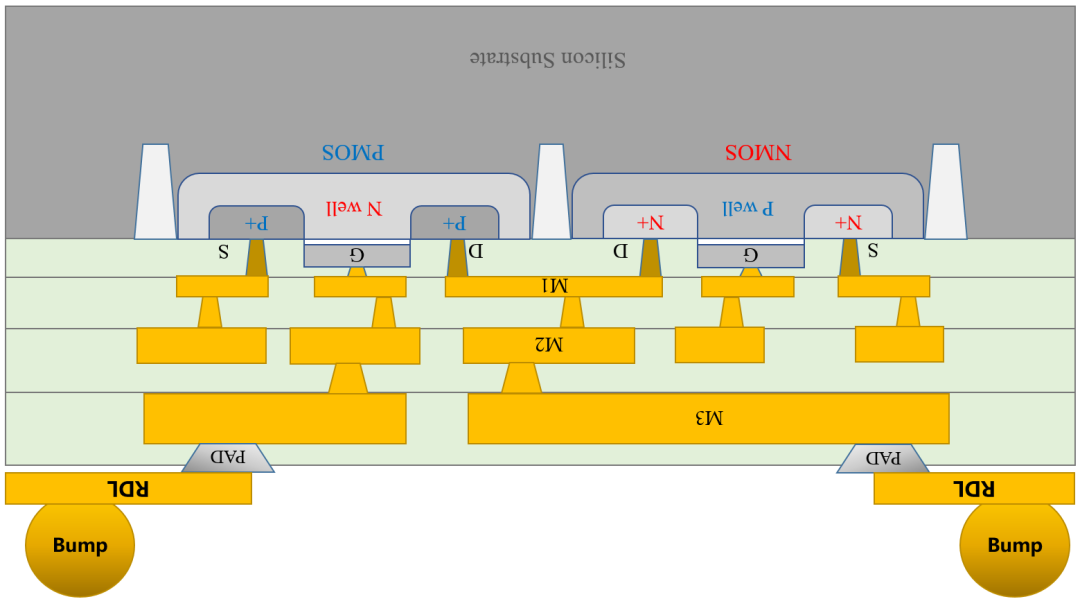

在芯片表面布线,通过RDL (Redistribution Layer) 重新布线层将PAD连接到占位更宽松的位置并制作凸点Bump,我们称之为XY平面的延伸。 然后通过Bump,芯片就可以直接安装在基板上了,这种工艺被称为倒装焊 Flip Chip,看看下面的图,你就会明白为啥叫倒装了。

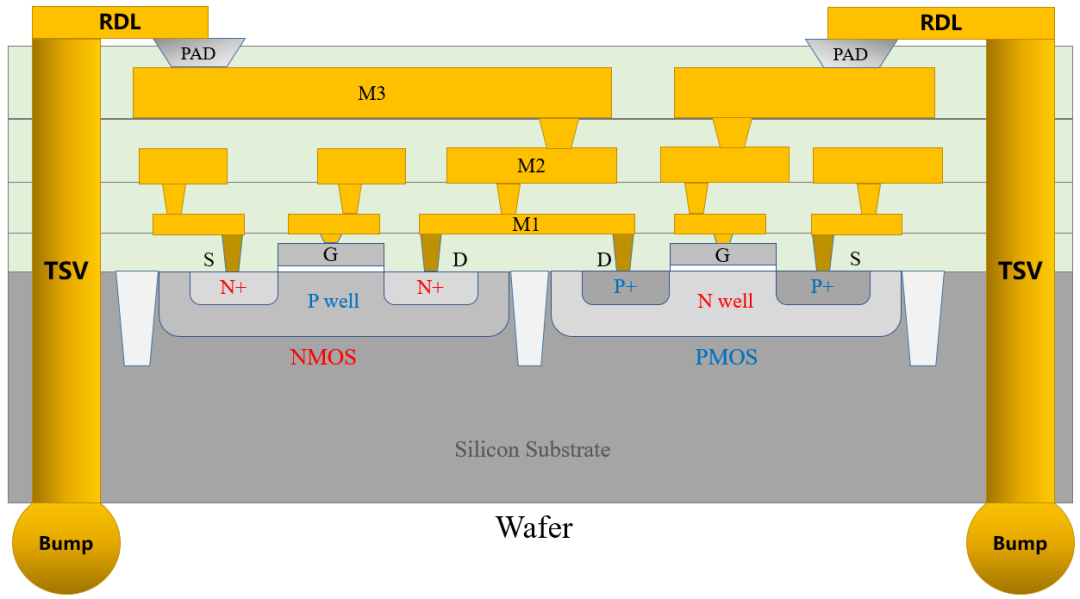

倒装焊工艺出现于上世纪60年代,和键合线基本是同时代的产物,历史已经很久了,我一般不称之为先进封装。 倒装焊芯片由于无法堆叠,因此无法进行Z轴的延伸,人们就发明出了能打穿整个芯片体的通孔技术,被称作TSV(Through Silicon Via)技术。 TSV有许多工艺难点需要克服,我认为最需要解决的是TSV的位置选择和孔径缩小。 因为TSV需要穿过整个芯片体,位置选择不好就会损坏内部的电路连接和晶体管,所以位置选择很重要。孔径的缩小也是为了尽可能少占芯片上的空间。毕竟1mm²面积可以安放一亿只以上的晶体管,弄不好几个亿一下子就没了。 不过,现在的TSV技术的发展也日益强大,据称可以在1mm²面积蚀刻出多达一百万个TSV,完全能满足高密度互连的需求。 下图就是芯片上的TSV示意图,通过TSV可将芯片上下表面通过金属导体连接起来,为芯片堆叠做好了准备。

在芯片上制作TSV实在是太难了,只有头部的Foundry厂可以做,这种TSV通常被称作3D TSV。 为了进一步提高集成度,人们又发明出了在硅基板Interposer上制作出TSV,被称作2.5D TSV。

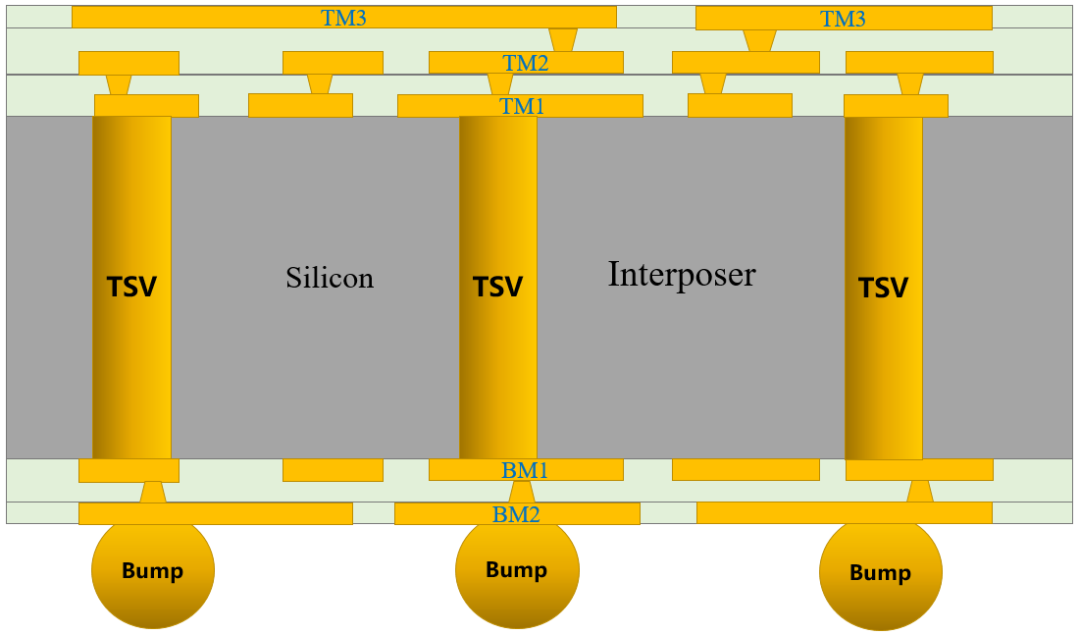

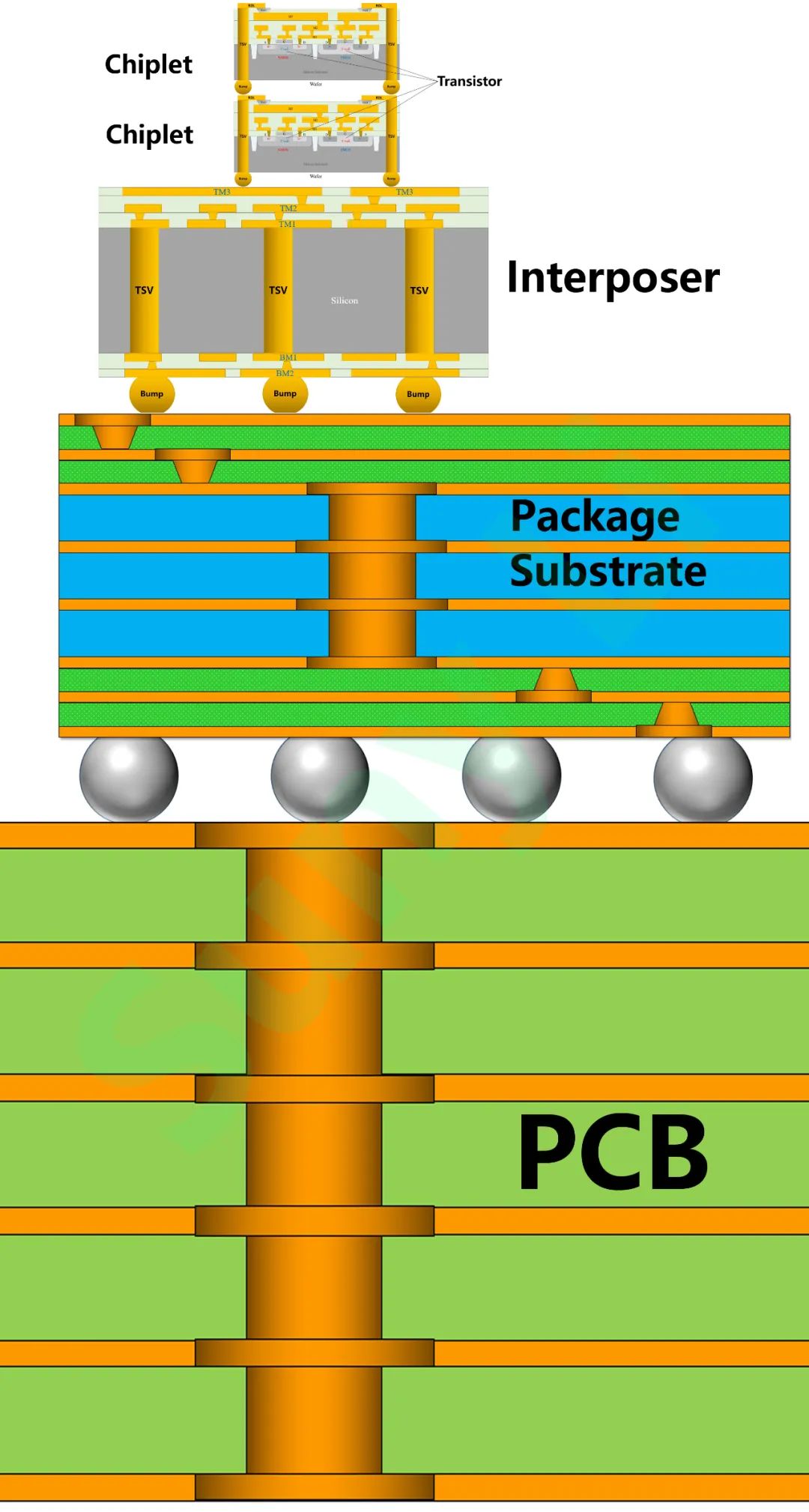

Interposer被称为硅转接板,插入器,可以提供比普通基板更高的互连密度。 下图所示为典型的硅转接板,上面3层金属,下面2层金属,中间通过硅通孔连接,我们称之为3+2结构。

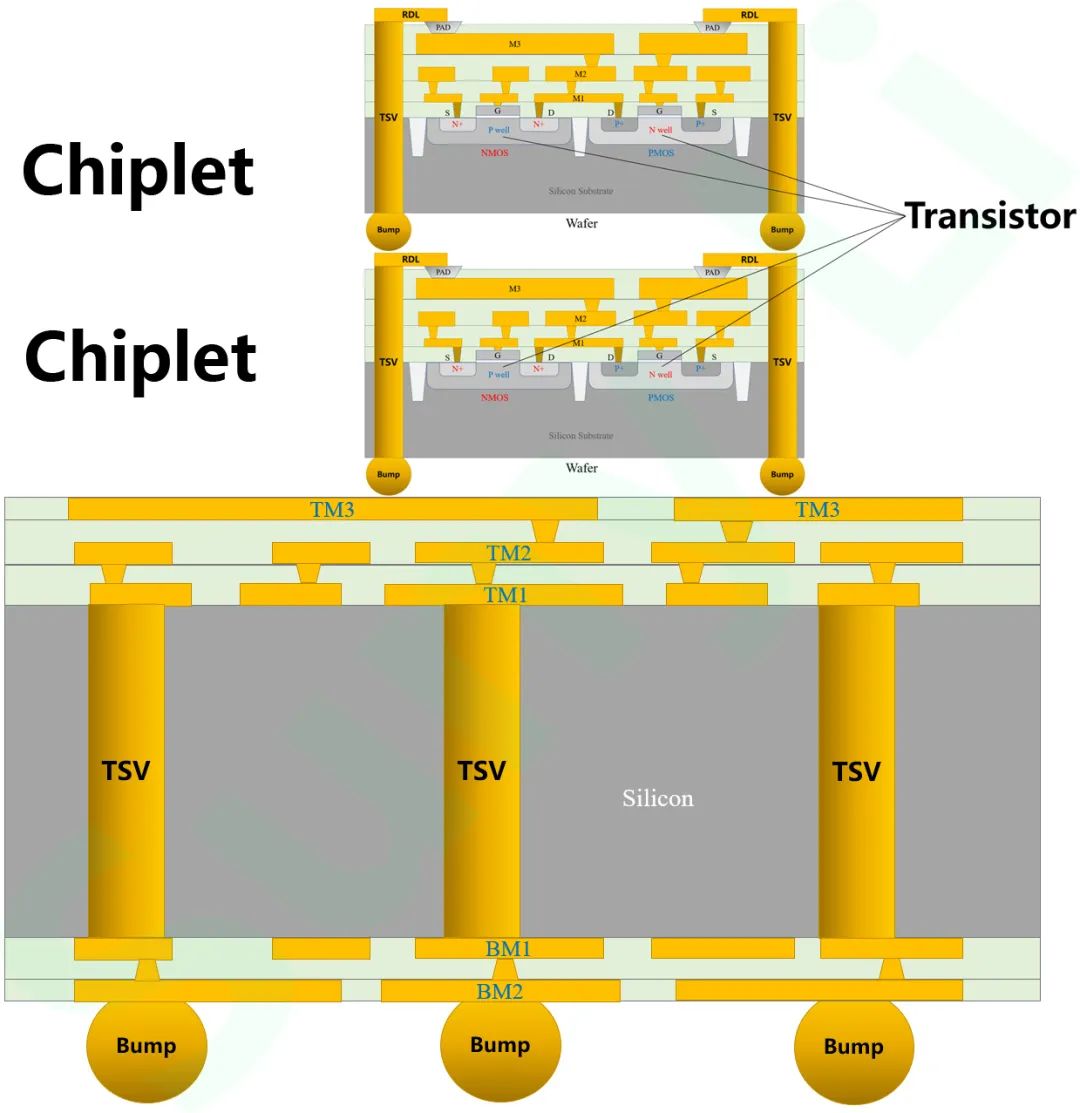

Interposer上的TSV通常比芯片上的TSV尺寸大一些、密度小一些,制作难度也要低一些,目前OSAT封测厂可以加工的就是此类2.5D TSV。 制作好Interposer,我们就可以将芯片或者芯粒安装在硅转接板上了。 如下图所示,因为结构上包含了3D TSV和2.5D TSV,因此我们称之为2.5D+3D先进封装。

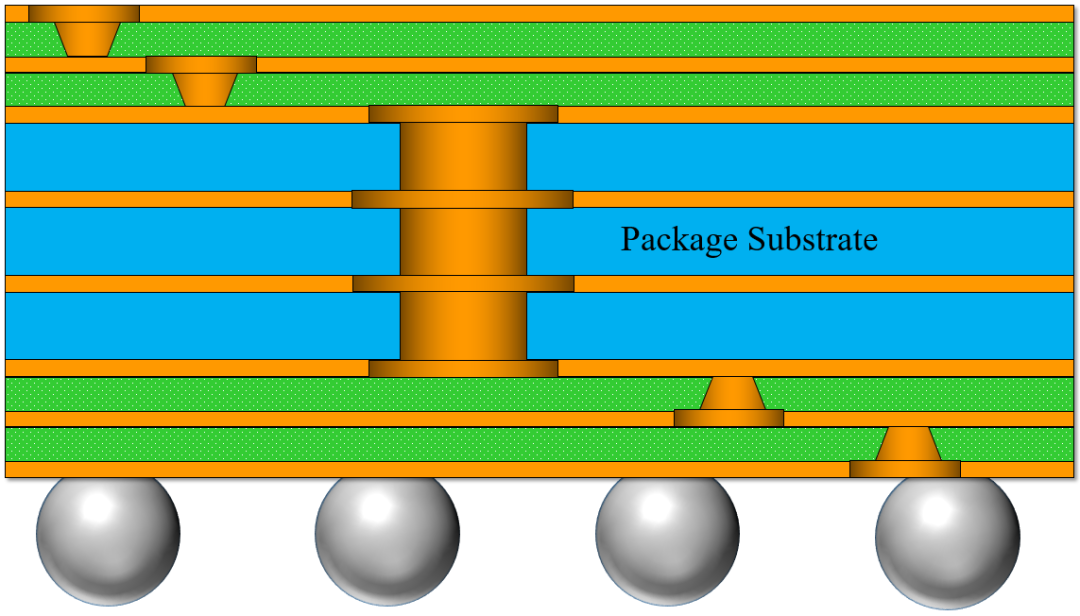

下一步,我们还需要制作封装基板Substrate,封装基板的材质种类比较多,可分为有机基板和陶瓷基板。 有机基板是由有机树脂和玻璃纤维布为主要材料制作而成,导体通常为铜箔。有机树脂通常包括:环氧树脂(FR4),BT树脂(双马来酰亚胺三嗪树脂),PPE树脂(聚苯醚树脂),PI树脂(聚酰亚胺树脂)等。 陶瓷基板相对有机基板有更好的机械性能和热性能,通常包含HTCC、LTCC、氮化铝等陶瓷基板。 下图所示为典型的有机基板结构,中间4层为Laminate层压法制作,上下表面的2层为Buildup积层法制造,我们称之为2+4+2结构。

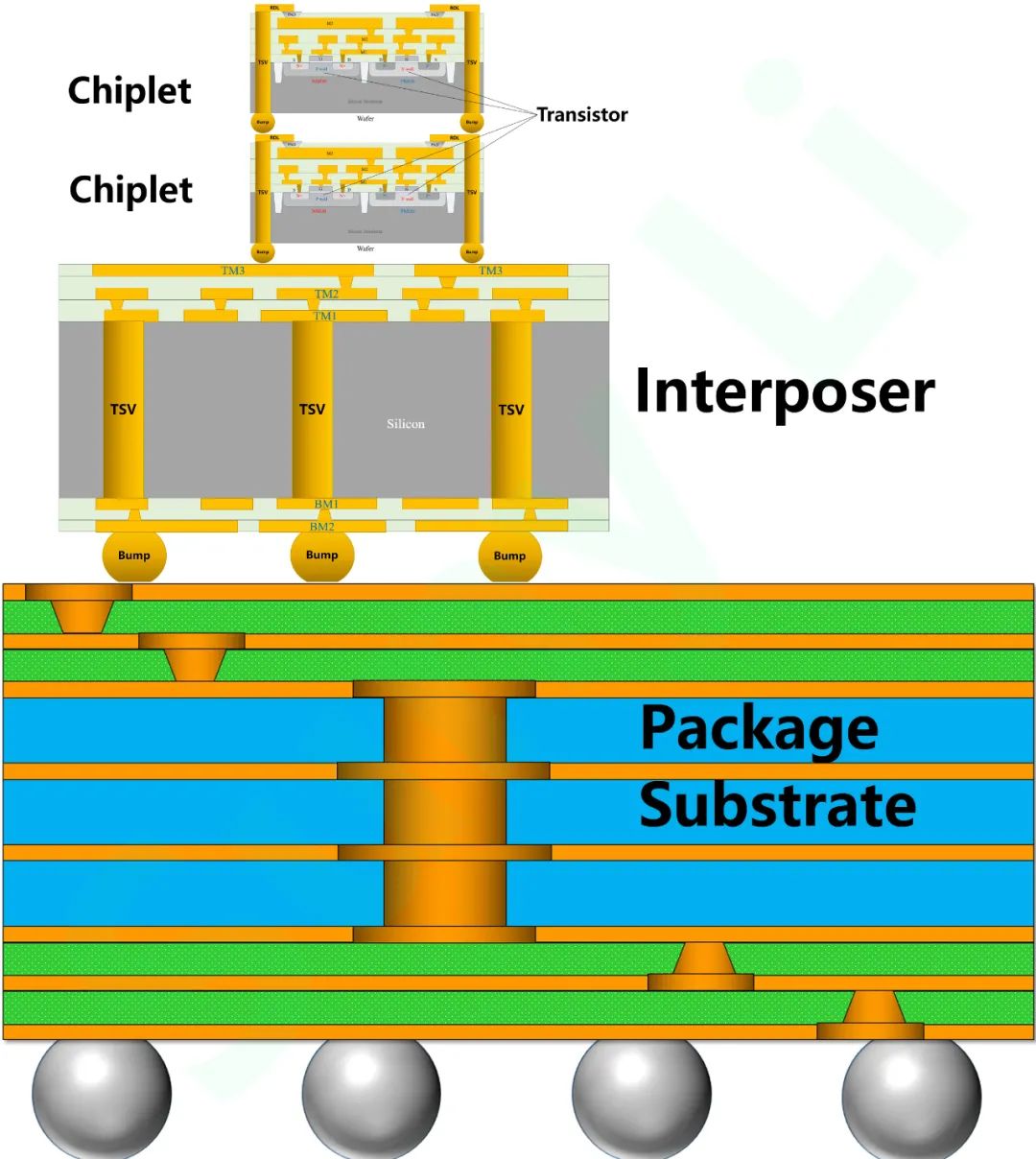

下面,我们将Chiplet、Inteposer、Substrate组装起来,并采用先进封装工艺进行处理,就形成了完整的先进封装。

芯片在封装内集成完成后,尺寸还不够大,另外有些分立元器件、例如大的电容、变压器等也无法集成到芯片封装内部,因此,对于电子产品来说,PCB始终是必不可少的。

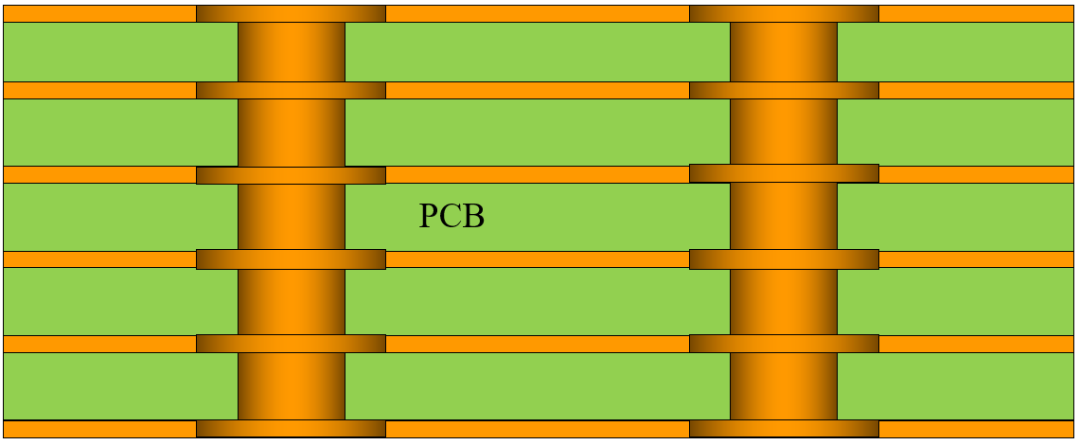

PCB的制造工艺和有机基板类似,其布线密度没有有机基板高,结构也相对比较简单。 PCB上多采用通孔结构,虽然现在高密度HDI板也采用了盲埋孔结构,但通孔由于结构简单,成本低廉,在PCB中得到了普遍的应用。 下图所示为6层通孔结构PCB,通过PCB,可将器件固定并进行电气互连。

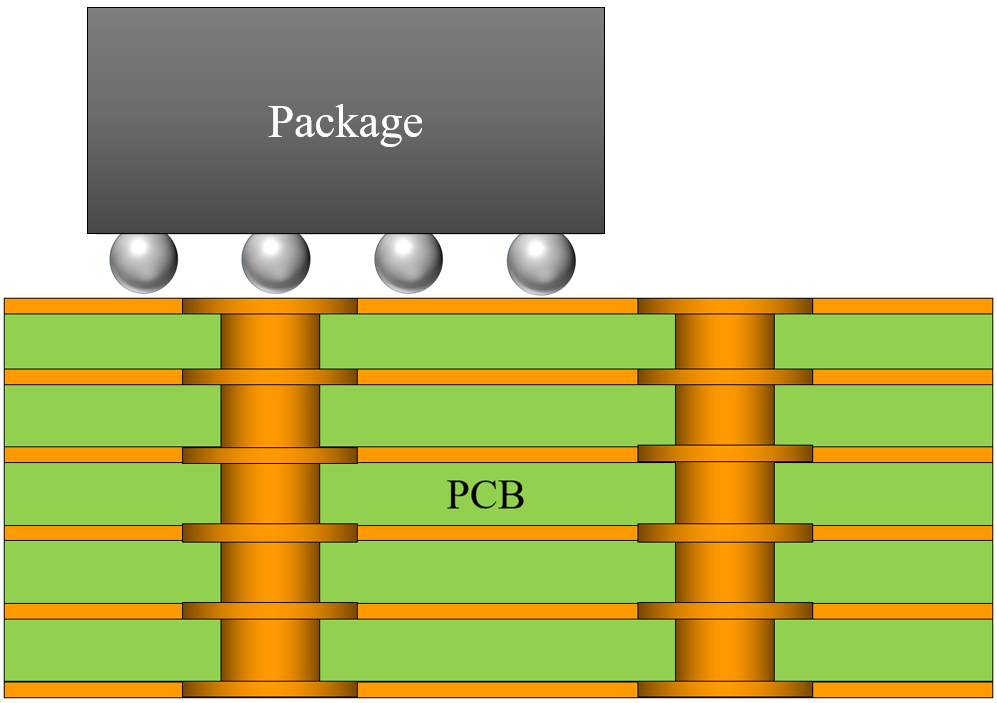

PCB加工好后,需要将封装好的元器件组装在PCB上,如下图所示,并通过PCB对外接插件和外部设备相连。

(这张图建议读者保存,因为这张图可能是业内第一张从晶体管到PCB的5级电路集成全图,由Suny Li手工绘制。因为是示意图,并未严格按照比例绘制,实际上,从晶体管到PCB,尺寸扩大了约1000000倍) 晶体管(NMOS或PMOS)在硅基底上制造完成后,通过接触孔连接到芯片上的金属布线,再连接到芯片的Pad,然后通过RDL连接到3DTSV,通过uBump连接到硅转接板上的RDL和2.5DTSV,再通过Bump连接到封装基板,然后通过封装基板上的连线和过孔连接到BGA,最后连接到PCB上的布线和过孔。 从晶体管到PCB,完整的5级电信号通路如下: Transitor→Contact→Copper→Pad→RDL¹→3DTSV→uBump→RDL²→2.5DTSV→Bump→Trace¹→Via¹→BGA→Trace²→Via²→PCB 在集成电路芯片上,人类通过晶体管实现了功能的创造,在SiP或先进封装上实现了功能的重构和尺度的放大,在PCB上进一步进行功能的重构和尺度的放大。 从晶体管到PCB,尺度放大了一百万倍,可以和人类自身的尺度相匹配。 最终,PCB和其他的部件有机地组合在一起,成为了现代人手中随时随地可以操作的手机和工作中基本无法离开的电脑。

在这篇文章中,我们从层次和环节两个方面来剖析现代电子集成技术。 我们将现代电子集成技术分为三个层次,芯片、封装、PCB,每个层次又分为不同的环节来详述。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

人类目前已知的118种元素中,来自自然界的元素有92种,其余的元素则是由人工合成的。代表元素的最小单位我们称之为原子,不同的原子构成了不同的物质。

芯片可用于创造更快、更节能的设备。这是因为这些PICs能够以最高的精度进行感应,并且在处理和传输数据

连接系统的性能产生不可接受的影响。 可分离性是我们希望使用连接器来促进子系统或系统部分的维护和级的原因

有限公司)-电源设计参考文档,对电源设计者有很大帮助,从基础知识到深入电源设计,由浅入深,便于学习。

在日前召开的2021 MWC上海展上,诺基亚贝尔移动网络事业部负责人薛瑞在接受C114采访时表示,诺基亚贝尔在整个5G

对于PLC程序的编写,我认为无须天马行空的标新立异,也无须花枝招展的炫弄技巧。只要在内容和质量这

把好关,具有正确性、可靠性、方便性、简洁性和可读性就是很好的程序! 一 PLC程序的内容

是因为小米9的后置摄像头采用了后置三摄的设计,设计较为复杂,对工艺要求较高,其中120度广角镜头的相关组件遭遇了良率不达标的问题;另一

或更多方完成一项任务所需采取的一系列步骤。证明者向验证者证明并使其相信自己知道或拥有某一消息,但证明过程不能向验证者泄露任何关于被证明消息的信息。

线路封装要求,提出了传递模结构设计的要.点,尤其对大型封装传递模的流道设计、注入压头结构、型腔设计和预防小岛移动等提出新的要

电路的应用 绿色环保已成为各行业发展一个定向趋势,如何做到环保且高效节能已成为当代热门话题。在

系统设计人员正面对着许多设计挑战,从实现数据转换器的接口到维持其系统与模拟系统接口时的信号保真度等。他们转向使用运算放大器来解决这些难题是很自然的事。

中电容器的正确选用 Correct Selection and Application of the Capacitors in Modern Power Supply Technology(PST)